3501 ED BLUESTEIN BLVD., AUSTIN, TEXAS 78721

### **Advance Information**

#### 64K-BIT DYNAMIC RAM

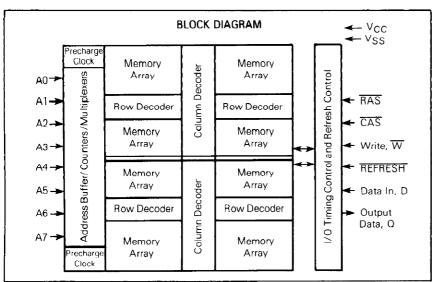

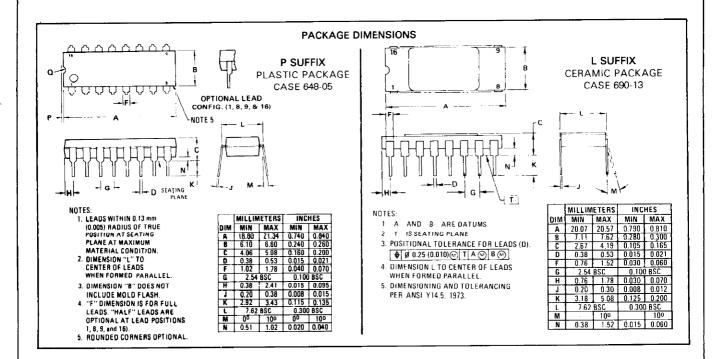

The MCM6664A is a 65,536 bit, high-speed, dynamic Random-Access Memory. Organized as 65,536 one-bit words and fabricated using HMOS high-performance N-channel silicon-gate technology, this new breed of 5-volt only dynamic RAM combines high performance with low cost and improved reliability.

By multiplexing row- and column-address inputs, the MCM6664A requires only eight address lines and permits packaging in standard 16-pin dual-in-line packages. Complete address decoding is done on chip with address latches incorporated. Data out is controlled by CAS allowing for greater system flexibility.

All inputs and outputs, including clocks, are fully TTL compatible. The MCM6664A incorporates a one-transistor cell design and dynamic storage techniques. In addition to the RAS-only refresh mode, the refresh control function available on pin 1 provides two additional modes of refresh, automatic and self refresh.

- Organized as 65,536 Words of 1 Bit

- Single 5 Volt Operation (± 10%)

- Maximum Access Time: MCM6664A-12 = 120 ns

MCM6664A-15 = 150 ns

MCM6664A-20 = 200 ns

- Low Power Dissipation 302.5 mW Maximum (A

- 302.5 mW Maximum (Active) (MCM6664A-15) 22 mW Maximum (Standby)

- Three-State Data Output

- Early-Write Common I/O Capability

- 16K Compatible 128-Cycle, 2 ms Refresh

- Control on Pin 1 for Automatic or Self Refresh

- RAS-only Refresh Mode

- CAS Controlled Output

- Fast Page Mode Cycle Time

- Low Soft Error Rate < 0.1% per 1000 Hours (See Soft Error Testing)

This document contains information on a new product. Specifications and information herein are subject to change without notice.

# **MCM6664A**

#### MOS

(N-CHANNEL, SILICON-GATE)

65,536-BIT DYNAMIC RANDOM ACCESS MEMORY

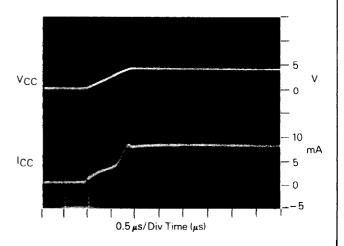

P SUFFIX

PLASTIC PACKAGE

CASE 648

L SUFFIX CERAMIC PACKAGE CASE 690

#### PIN ASSIGNMENT

| * REFRESH               | 10 | 16 | Vss |

|-------------------------|----|----|-----|

| Dζ                      | 2  | 15 | CAS |

| $\overline{\mathbf{w}}$ | 3  | 14 | Q   |

| RAS                     | 4  | 13 | A6  |

| A0 🕻                    | 5  | 12 | А3  |

| A2 <b>[</b>             | 6  | 11 | A4  |

| A1 <b>I</b>             | 7  | 10 | A5  |

| Vcc <b>t</b>            | 8  | 9  | Α7  |

\*If pin is not used, it should be connected to VCC through a 10 k resistor.

| PIN NAMES                |       |  |  |  |  |

|--------------------------|-------|--|--|--|--|

| REFRESH Ref              | fresh |  |  |  |  |

| A0-A7 Address I          | nput  |  |  |  |  |

| D                        | ta In |  |  |  |  |

| Q                        | Out   |  |  |  |  |

| W Read/Write I           | nput  |  |  |  |  |

| RASRow Address St        | robe  |  |  |  |  |

| CAS Column Address St    | robe  |  |  |  |  |

| V <sub>CC</sub> Power (+ | 5 V)  |  |  |  |  |

| V <sub>S</sub> SGro      | ound  |  |  |  |  |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

©MOTOROLA INC., 1982

ADI-875 R1

#### ABSOLUTE MAXIMUM RATINGS (See Note)

| Rating                                          | Symbol                             | Value       | Unit |

|-------------------------------------------------|------------------------------------|-------------|------|

| Voltage on Any Pin Relative to VSS (except VCC) | V <sub>in</sub> , V <sub>out</sub> | 2 to +7     | V    |

| Voltage on VCC Supply Relative to VSS           | Vcc                                | -1  to  +7  | V    |

| Operating Temperature Range                     | TA                                 | 0 to +70    | °C   |

| Storage Temperature Range                       | Tstg                               | -65 to +150 | °C   |

| Power Dissipation                               | PD                                 | 1.0         | W    |

| Data Out Current (Short Circuit)                | lout                               | 50          | mA   |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

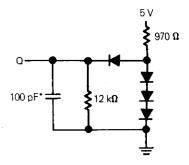

#### FIGURE 1 — OUTPUT LOAD

\*Includes Jig Capacitance

# DC OPERATING CONDITIONS AND CHARACTERISTICS (Full operating voltage and temperature range unless otherwise noted.)

#### RECOMMENDED OPERATING CONDITIONS

| Paramete                    | r                     | Symbol          | Min   | Тур | Max                | Unit | Notes |

|-----------------------------|-----------------------|-----------------|-------|-----|--------------------|------|-------|

| Supply Voltage              | MCM6664A-12, -15, -20 | Vcc             | 4.5   | 5.0 | 5.5                | V    | 1     |

|                             |                       | VSS             | 0     | 0   | 0                  | V    | 1     |

| Logic 1 Voltage, All Inputs |                       | VIH             | 2.4   |     | V <sub>CC</sub> +1 | V    | 1     |

| Logic 0 Voltage, All Inputs |                       | V <sub>IL</sub> | - 1.0 | _   | 8.0                | V    | 1, 19 |

#### DC CHARACTERISTICS

| Characteristic                                                                                                                                       | Symbol           | Min         | Max                   | Units | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|-----------------------|-------|-------|

| VCC Power Supply Current (Standby)                                                                                                                   | lcc2             | -           | 4.0                   | mA    | 5     |

| V <sub>CC</sub> Power Supply Current<br>6664A-12, t <sub>RC</sub> = 250<br>6664A-15, t <sub>RC</sub> = 270<br>6664A-20, t <sub>RC</sub> = 330        | <sup>1</sup> CC1 | -<br>-      | 60<br>55<br>50        | mA    | 4     |

| $V_{CC}$ Power Supply Current During $\overline{RAS}$ only Refresh Cycles 6664A-12, $t_{RC}$ = 250 6664A-15, $t_{RC}$ = 270 6664A-20, $t_{RC}$ = 330 | ICC3             | _<br>_<br>_ | 50<br>45<br><b>40</b> | mA    | 4     |

| Input Leakage Current (VSS≤Vin≤VCC) (Any Input Except REFRESH)                                                                                       | 1(L)             | -           | 10                    | μΑ    | _     |

| REFRESH Input Current (VSS≤Vin≤VCC)                                                                                                                  | l(F)             |             | 20                    | μΑ    |       |

| Output Leakage Current (CAS at logic 1, 0≤V <sub>out</sub> ≤5.5)                                                                                     | <u> </u>  O(L)   |             | 10                    | μΑ    |       |

| Output Logic 1 Voltage @ I <sub>Out</sub> = -4 mA                                                                                                    | Voн              | 2.4         | -                     | V     |       |

| Output Logic 0 Voltage @ I <sub>out</sub> = 4 mA                                                                                                     | V <sub>OL</sub>  | -           | 0.4                   | V     |       |

#### CAPACITANCE (f = 1.0 MHz, TA = 25°C, VCC = 5 V Periodically Sampled Rather Than 100% Tested)

| Parameter                                                             | Symbol          | Тур | Max | Unit | Notes |

|-----------------------------------------------------------------------|-----------------|-----|-----|------|-------|

| Input Capacitance (A0-A7), D                                          | C <sub>I1</sub> | 3   | 5   | ρF   | 7_    |

| Input Capacitance RAS, CAS, WRITE, REFRESH                            | C <sub>I2</sub> | 6   | 8   | рF   | 7     |

| Output Canacitance (O) $(\overline{CAS} = V_{IM})$ to disable output) | Co              | 5   | 7   | ρF   | 7     |

- NOTES: 1. All voltages referenced to VSS.

- 2. VIH min and VIL max are reference levels for measuring timing of input signals. Transition times are measured between VIH and VII.

- 3. An initial pause of 100 µs is required after power-up followed by any 8 RAS cycles before proper device operation guaranteed.

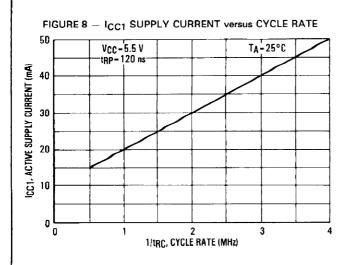

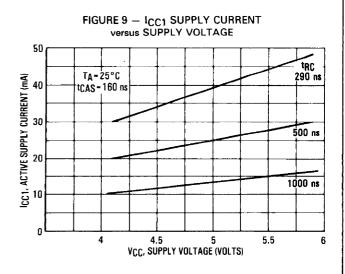

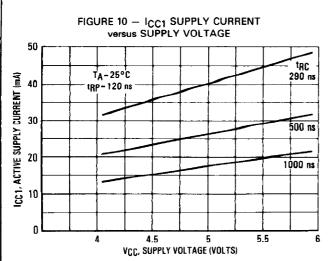

- 4. Current is a function of cycle rate and output loading; maximum current is measured at the fastest cycle rate with the output open.

- 5. RAS and CAS are both at a logic 1.

- The transition time specification applies for all inputs signals. In addition to meeting the transition rate specification, all input signals must transmit between V<sub>IH</sub> and V<sub>IH</sub> (or between V<sub>IH</sub> and V<sub>IH</sub>) in a monotonic manner.

- 7. Capacitance measured with a Boonton Meter or effective capacitance calculated from the equation:  $C = \frac{i\Delta V}{\Delta V}$

- The specifications for t<sub>RC</sub> (min), and t<sub>RWC</sub> (min) are used only to indicate cycle time at which proper operation over the full temperature range (0°C≤T<sub>A</sub>≤70°C) is assured.

- 9. AC measurements  $t_T = 5.0$  ns.

- 10. Assumes that  $t_{RCD} \le t_{RCD}$  (max).

- 11. Assumes that t<sub>RCD</sub>≥t<sub>RCD</sub> (max)

- 12. Measured with a current load equivalent to 2 TTL ( $-200 \mu A$ , +4 mA) loads and 100 pF ( $V_{OH} = 2.0 \text{ V}$ ,  $V_{OL} = 0.8 \text{ V}$ ).

- 13. Operation within the tRCD (max) limit ensures that tRAC (max) can be met. tRCD (max) is specified as a reference point only; if tRCD is greater than the specified tRCD(max) limit, then access time is controlled exclusively by tCAC.

# AC OPERATING CONDITIONS AND CHARACTERISTICS (Read, Write, and Read-Modify-Write Cycles) (Full Operating Voltage and Temperature Range Unless Otherwise Noted . See Notes 2, 3, 6, and Figure 1)

|                                                     |                  | 6664     | A-12                                             | 6664     | A-15         | 6664 | 4A-20    |                                                  | 1                                                |

|-----------------------------------------------------|------------------|----------|--------------------------------------------------|----------|--------------|------|----------|--------------------------------------------------|--------------------------------------------------|

| Parameter                                           | Symbol           | Min      | Max                                              | Min      | Max          | Min  | Max      | Units                                            | Notes                                            |

| Random Read or Write Cycle Time                     | †RC              | 250      |                                                  | 270      | _            | 330  | _        | ns                                               | 8, 9                                             |

| Read Write Cycle Time                               | †RWC             | 255      | _                                                | 280      | _            | 345  | _        | ns                                               | 8, 9                                             |

| Access Time from Row Address Strobe                 | tRAC             | _        | 120                                              |          | 150          |      | 200      | ns                                               | 10, 12                                           |

| Access Time from Column Address Strobe              | tCAC             |          | 60                                               | _        | 75           |      | 100      | ns                                               | 11, 12                                           |

| Output Buffer and Turn-Off Delay                    | toff             | 0        | 30                                               | 0        | 30           | 0    | 40       | ns                                               | 18                                               |

| Row Address Strobe Precharge Time                   | tRP              | 100      | _                                                | 100      | _            | 120  | _        | ns                                               | _                                                |

| Row Address Strobe Pulse Width                      | tRAS             | 120      | 10000                                            | 150      | 10000        | 200  | 10000    | ns                                               |                                                  |

| Column Address Strobe Pulse Width                   | tCAS             | 60       | 10000                                            | 75       | 10000        | 100  | 10000    | ns                                               |                                                  |

| Row to Column Strobe Lead Time                      | tRCD             | 20       | 60                                               | 25       | 75           | 30   | 100      | ns                                               | 13                                               |

| Row Address Setup Time                              | tASR             | 0        | _                                                | 0        |              | 0    | _        | ns                                               |                                                  |

| Row Address Hold Time                               | tRAH             | 15       | _                                                | 20       |              | 25   |          | ns                                               | 1 _                                              |

| Column Address Setup Time                           | tASC             | 0        |                                                  | 0        |              | 0    |          | ns                                               | <del> </del>                                     |

| Column Address Setup Time  Column Address Hold Time |                  | 25       |                                                  | 35       | _            | 45   |          | ns                                               |                                                  |

| Column Address Hold Time Referenced to RAS          | t <sub>CAH</sub> | 85       |                                                  | 95       | _            | 120  |          | ns                                               | 17                                               |

| Transition Time (Rise and Fall)                     | t <sub>T</sub>   | 3        | 50                                               | 3        | 50           | 3    | 50       | ns                                               | 6                                                |

|                                                     |                  | 0        | - 50                                             | 0        | - 50         | 0    | -        | ns                                               | -                                                |

| Read Command Setup Time                             | tRCS             | 0        | <del> </del>                                     | 0        |              | 0    | _        | ns                                               | 14                                               |

| Read Command Hold Time                              | tRCH             | 0        |                                                  | 0        |              | 0    |          | ns                                               | 14                                               |

| Read Command Hold Time Referenced to RAS            | <sup>t</sup> RRH | 25       |                                                  | 35       |              | 45   | _        | ns                                               | <del>- ' -</del>                                 |

| Write Command Hold Time                             | tWCH             | 85       |                                                  | 95       |              | 120  |          | ns                                               | 17                                               |

| Write Command Hold Time Referenced to RAS           | tWCR             | 25       |                                                  | 35       | _            | 45   | _        | ns                                               | <del>                                     </del> |

| Write Command Pulse Width                           | tWP              | <b></b>  |                                                  | 45       | <del>-</del> | 55   |          | <del>                                     </del> | ┝▔                                               |

| Write Command to Row Strobe Lead Time               | tRWL             | 40       | -                                                | 45       |              | 55   |          | ns                                               | <del></del> -                                    |

| Write Command to Column Strobe Lead Time            | tCWL             | <u> </u> | <del>                                     </del> | -        | ├──          | 0    |          | <del> </del>                                     | 15                                               |

| Data in Setup Time                                  | t <sub>DS</sub>  | 0        | <del></del>                                      | 0        |              | 45   | _        | ns                                               | 15                                               |

| Data in Hold Time                                   | <sup>†</sup> DH  | 25       |                                                  | 35       | _            |      |          | ns                                               |                                                  |

| Data in Hold Time Referenced to RAS                 | †DHR_            | 85       | <del>  -</del>                                   | 95       |              | 120  |          | ns                                               | 17                                               |

| Column to Row Strobe Precharge Time                 | †CRP             | 10       | _                                                | - 10     |              | - 10 | _        | ns                                               | <del>  -</del>                                   |

| RAS Hold Time                                       | tRSH_            | 60       |                                                  | 75       | -            | 100  |          | ns                                               | <del>  -</del>                                   |

| Refresh Period                                      | tresh            | -        | 2.0                                              | -        | 2.0          | - 10 | 2.0      | ms                                               | 10                                               |

| WRITE Command Setup Time                            | twcs             | - 10     |                                                  | <u> </u> |              | 10   |          | ns                                               | 16                                               |

| CAS to WRITE Delay                                  | tCMD             | 40       |                                                  | 45       | _            | 55   |          | ns                                               | 16                                               |

| RAS to WRITE Delay                                  | †RWD             | 100      |                                                  | 120      | -            | 155  | _        | ns                                               | 16                                               |

| CAS Hold Time                                       | tcsh             | 120      |                                                  | 150      |              | 200  | _        | ns                                               |                                                  |

| CAS Precharge Time (Page Mode Cycle Only)           | tCP              | 50       | <u> </u>                                         | 60       |              | 80   | _        | ns                                               | <del>-</del> -                                   |

| Page Mode Cycle Time                                | †PC              | 120      |                                                  | 145      |              | 200  |          | ns                                               | <del>  -</del>                                   |

| RAS to REFRESH Delay                                | <u>tred</u>      | - 10     | ļ                                                | - 10     |              | - 10 | <u> </u> | ns                                               |                                                  |

| REFRESH Period (Battery Backup Mode)                | †FBP_            | 2000     |                                                  | 2000     | _            | 2000 |          | ns                                               | <del>-</del>                                     |

| REFRESH to RAS Precharge Time (Battery Backup Mode) | t <sub>FBR</sub> | 290      |                                                  | 320      |              | 400  | _        | ns                                               | ļ <u> </u>                                       |

| REFRESH Cycle Time (Auto Pulse Mode)                | tFC              | 250      |                                                  | 270      | _            | 330  |          | ns                                               | <del>↓</del>                                     |

| REFRESH Pulse Period (Auto Period Mode)             | tFP              | 60       | 2000                                             | 60       | 2000         | 60   | 2000     | ns                                               | <del>  -</del>                                   |

| REFRESH to RAS Setup Time (Auto Pulse Mode)         | †FSR             | -30      | -                                                | - 30     | <u> </u>     | - 30 | _        | ns                                               |                                                  |

| REFRESH to RAS Delay Time (Auto Pulse Mode)         | t <sub>FRD</sub> | 290      |                                                  | 320      |              | 400  |          | ns                                               |                                                  |

| REFRESH Inactive Time                               | tFI              | 60       |                                                  | 60       |              | 60   | _        | ns                                               | <u> </u>                                         |

| RAS to REFRESH Lead Time                            | terl             | 350      | _                                                | 370      |              | 450  |          | ns                                               |                                                  |

| RAS Inactive Time During REFRESH                    | tFRI             | 350      | -                                                | 370      | -            | 450  |          | ns                                               | -                                                |

- 14. Either t<sub>RRH</sub> or t<sub>RCH</sub> must be satisfied for a read cycle.

- 15. These parameters are referenced to CAS leading edge in random write cycles and to WRITE leading edge in delayed write or read-modify-write cycles.

- 16. t<sub>WCS</sub>, t<sub>CWD</sub> and t<sub>RWD</sub> are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only; if t<sub>WCS</sub>≥t<sub>WCS</sub> (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle; if t<sub>CWD</sub>≥t<sub>CWD</sub> (min) and t<sub>RWD</sub>≥t<sub>RWD</sub> (min), the cycle is read-write cycle and the data out will contain data read from the selected cell; if neither of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

- 17. tAR min ≤ tAR=tRCD+tCAH, tDHR min ≤ tDHR=tRCD+tDH, tWCR min ≤ tWCR=tRCD+tWCH

- 18. toff (max) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- 19. The device will withstand undershoots to the -2 volt level with a maximum pulse width of 20 ns at the -1.5 volt level. This is periodically sampled rather than 100% tested.

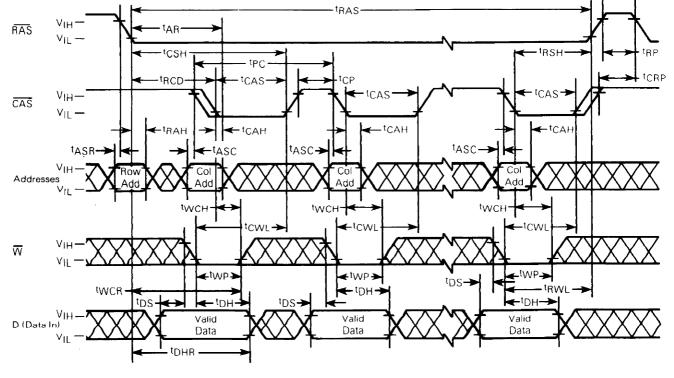

## PAGE MODE WRITE CYCLE

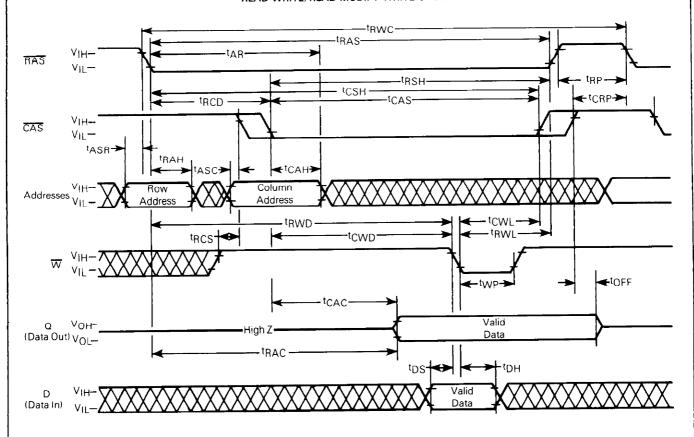

#### READ-WRITE/READ-MODIFY-WRITE CYCLE

# SELF REFRESH MODE (Battery Backup)\* RAS $V_{\text{IH}}-$ REFRESH VIL-AUTOMATIC PULSE REFRESH CYCLE — SINGLE PULSE\* RAS VIH-REFRESH VIL-AUTOMATIC PULSE REFRESH CYCLE - MULTIPLE PULSE\* RAS REFRESH VIH-\*Addresses, data-in and WRITE are don't care.

#### TYPICAL CHARACTERISTICS

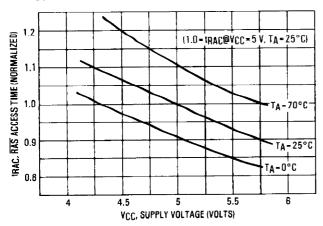

FIGURE 2 - RAS ACCESS TIME versus SUPPLY VOLTAGE

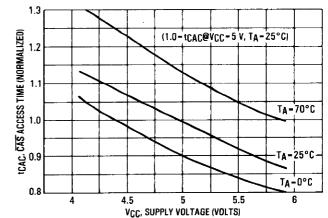

FIGURE 3 — CAS ACCESS TIME versus SUPPLY VOLTAGE

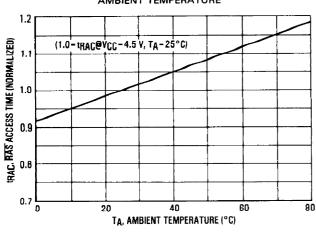

FIGURE 4 — RAS ACCESS TIME versus AMBIENT TEMPERATURE

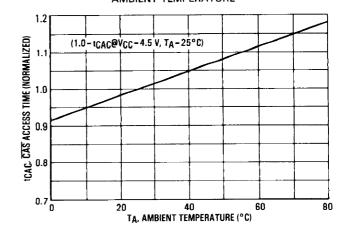

FIGURE 5 — CAS ACCESS TIME versus

AMBIENT TEMPERATURE

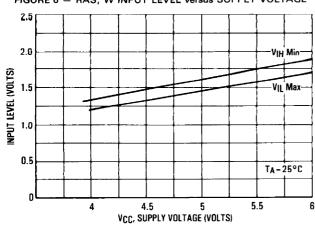

FIGURE 6 - RAS, W INPUT LEVEL versus SUPPLY VOLTAGE

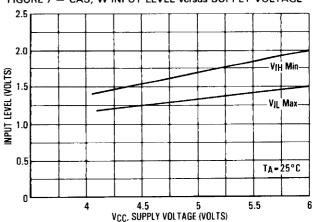

FIGURE 7 - CAS, W INPUT LEVEL versus SUPPLY VOLTAGE

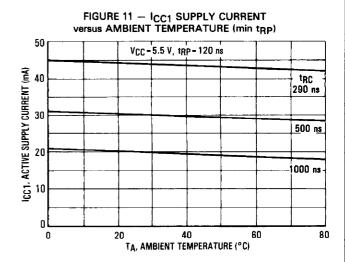

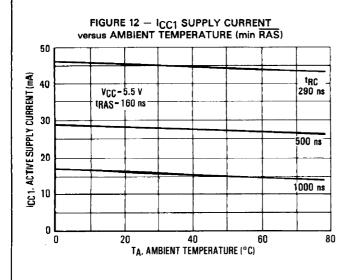

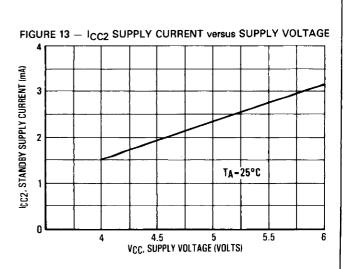

#### TYPICAL CHARACTERISTICS (continued)

#### TYPICAL CHARACTERISTICS (continued)

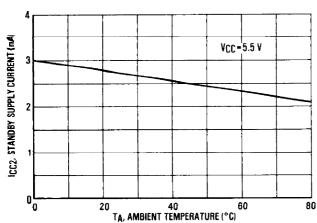

FIGURE 14 - ICC2 STANDBY CURRENT versus AMBIENT TEMPERATURE

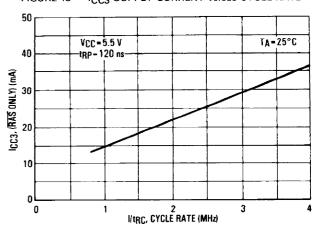

FIGURE 15 - ICC3 SUPPLY CURRENT versus CYCLE RATE

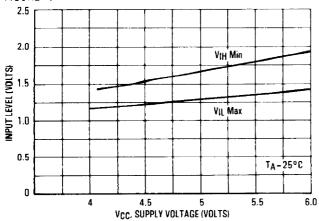

FIGURE 16 - ADDRESS INPUT LEVEL versus SUPPLY VOLTAGE

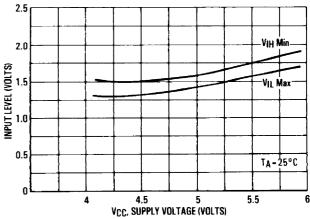

FIGURE 17 — DATA INPUT LEVEL versus SUPPLY VOLTAGE 2.5

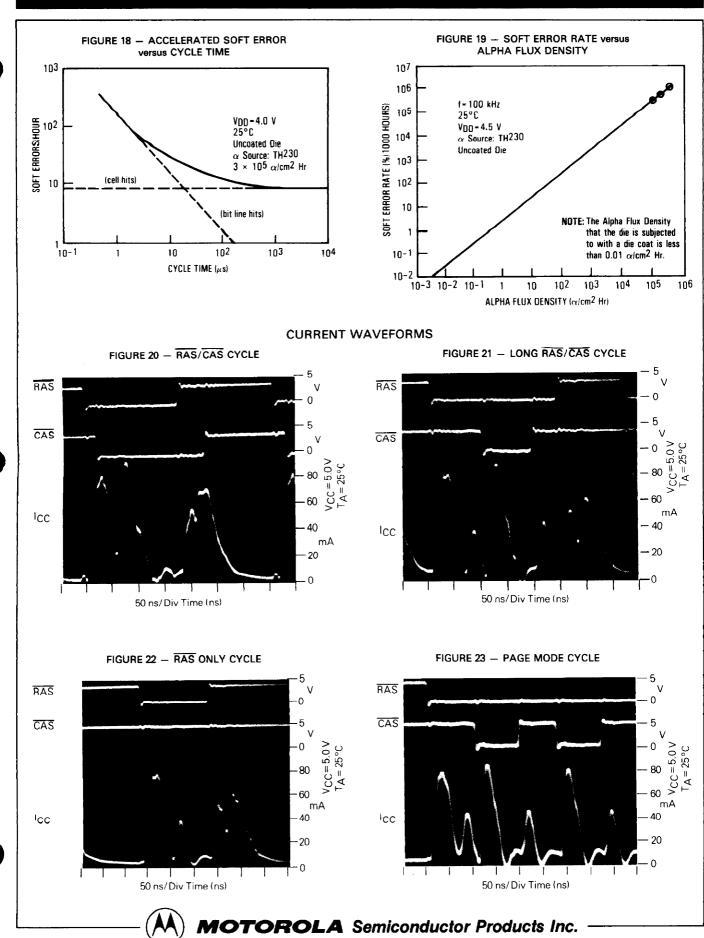

#### SOFT ERROR TESTING

The storage cell depletion regions as well as the sense amplifier and its associated bit lines are susceptible to charge collection of electrons from an alpha "hit." However, the susceptibility of these vulnerable regions varies. Depleted storage cells are vulnerable at all times, whereas the sense amplifiers and associated bit lines are susceptible only during the small portion of the memory cycle just prior to sensing. Hence, an increase in the frequency of dynamic RAM access will cause a corresponding increase in the soft error rate.

To take this memory access dependency into account, the total soft error rate profile includes a cycle time component. The soft error rate due to bit line hits at the system's memory cycle rate is added to the soft error rate due to storage cell hits which are not frequency dependent. Figure 18 illustrates the impact that frequency of access has on the MCM6664A/MCM6665A overall soft error rate.

Under normal operating conditions, the die will be exposed to radiation levels of less than 0.01 alpha/cm<sup>2</sup>/hr. Accelerated soft error testing data is generated from at least three high-intensity sources having an Alpha Flux Density range of  $1 \times 10^5$  to  $6 \times 10^5$  (alpha/cm<sup>2</sup>hr) placed over uncoated die. Figure 19 shows the soft error rate for a given alpha flux density at a cycle rate of 100 kHz. The accelerated data of Figures 18 and 19 project that the soft error rate for package level radiation will be less than 0.1%/1000 hours.

#### SYSTEM LIFE OPERATING TEST CONDITIONS

- 1) Cycle time: 1 microsecond for read, write and refresh cycles

- 2) Refresh Rate: 1 millisecond

- 3) Voltage: 5.0 V

- 4) Temperature: 30° C ±2° C (ambient temperature inside enclosure)

- 5) Elevation: Approximately 620 feet above mean sea level

- 6) Data Patterns: Write the entire memory space sequentially with all "1"s and then perform continuous sequential reads for 6 hours. Next, write the entire memory space with all "0"s sequentially and then perform continuous sequential reads for 6 hours. Next, go back to the all "1"s pattern and repeat the sequences all over again.

#### **DEVICE INITIALIZATION**

Since the 64K dynamic RAM is a single supply 5 V only device, the need for power supply sequencing is no longer required as was the case in older generation dynamic RAMs. On power-up an initial pause of 100 microseconds is required for the internal substrate generator pump to establish the correct bias voltage. This is to be followed by a minimum of eight active cycles of the row address strobe (clock) to initialize the various dynamic nodes internal to the device. During an extended inactive state of the device (greater than 2 ms with device powered up) the wake up sequence (8 active cycles) will be necessary to assure proper device operation. See Figures 25 and 26 for power on characteristics of the RAM for two conditions (clocks active, clocks inactive)

The row address strobe is the primary "clock" that activates the device and maintains the data when the RAM is in the standby mode. This is the main feature that distinquishes it as a dynamic RAM as opposed to a static RAM. A dynamic RAM is placed in a low power standby mode when the device receives a positive-going row address strobe. The variation in the power dissipation of a dynamic RAM from the active to the standby state is an order of magnitude or more for NMOS devices. This feature is used to its fullest advantage with high density mainframe memory systems, where only a very small percentage of the devices are in the active mode at any one time and the rest of the devices are in the standby mode. Thus, large memory systems can be assembled that dissipate very low power per bit compared to a system where all devices are active continuously.

#### ADDRESSING THE RAM

The eight address pins on the device are time multiplexed with two separate 8-bit address fields that are strobed at the beginning of the memory cycle by two clocks (active

negative) called the row address strobe and the column address strobe. A total of sixteen address bits will decode one of the 65,536 cell locations in the device. The column address strobe follows the row address strobe by a specified minimum and maximum time called "tRCD," which is the row to column strobe delay. This time interval is also referred to as the multiplex window which gives flexibility to a system designer to set up his external addresses into the RAM. These conditions have to be met for normal read or write cycles. This initial portion of the cycle accomplishes the normal addressing of the device. There are, however, two other variations in addressing the 64K RAM, one is called the page mode cycle (described later) where an 8-bit column address field is presented on the input pins and latched by the CAS clock; and the other is the RAS only refresh cycle (described later) where a 7-bit row address field is presented on the input pins and latched by the RAS clock. In the latter case, the most significant bit on Row Address A7 (pin 9) is not required for refresh. See bit address map for the topology of the cells and their address selection.

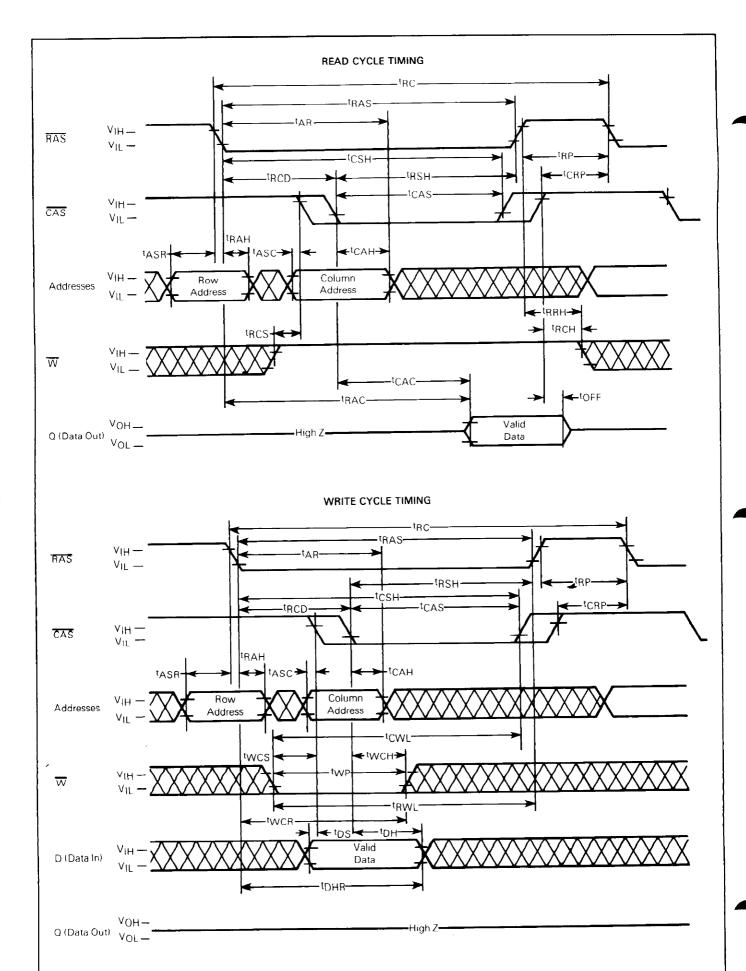

#### **NORMAL READ CYCLE**

A read cycle is referred to as normal read cycle to differentiate if from a page-mode-read cycle, a read-while-write cycle, and read-modify-write cycle which are covered in a later section.

The memory read cycle begins with the row addresses valid and the  $\overline{RAS}$  clock transitioning from  $V_{IH}$  to the  $V_{IL}$  level. The  $\overline{CAS}$  clock must also make a transition from  $V_{IH}$  to the  $V_{IL}$  level at the specified tRCD timing limits when the column addresses are latched. Both the  $\overline{RAS}$  and  $\overline{CAS}$  clocks trigger a sequence of events which are controlled by several delayed internal clocks. Also, these clocks are linked in such a manner that the access time of the device is independent of the address multiplex window. The only stipulation is that the  $\overline{CAS}$  clock must be active before or at

#### **CURRENT WAVEFORMS**

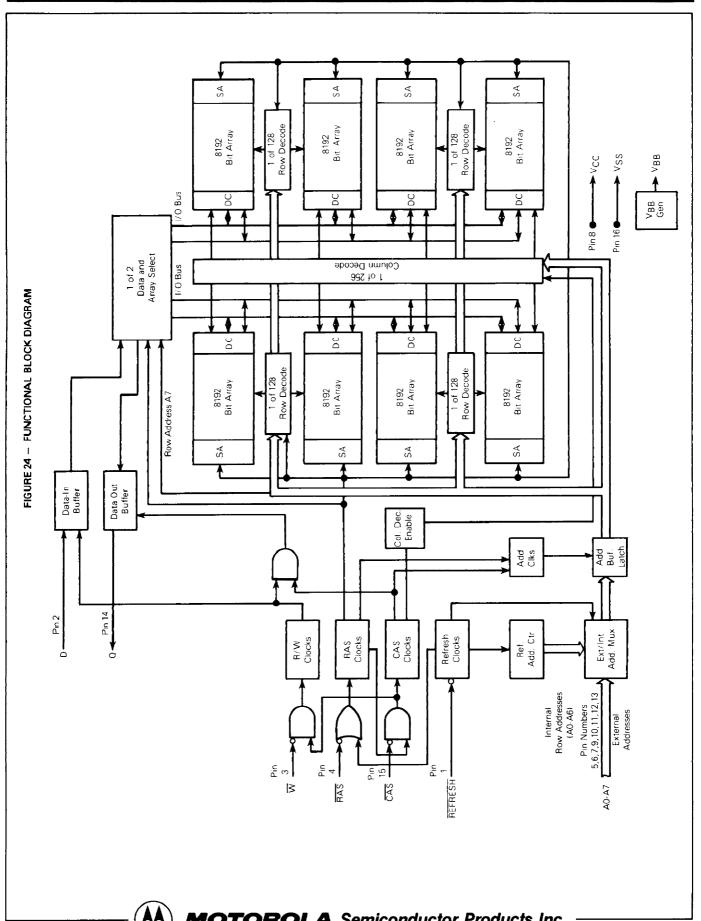

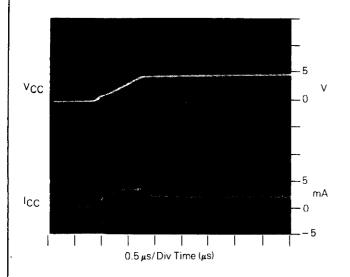

FIGURE 25 — SUPPLY CURRENT VERSUS SUPPLY VOLTAGE DURING POWER UP, RAS, CAS = VCC

FIGURE 26 — SUPPLY CURRENT VERSUS SUPPLY VOLTAGE DURING POWER UP, RAS, CAS = VSS

the tRCD maximum specification for an access (data valid) from the RAS clock edge to be guaranteed (tRAC). If the tRCD maximum condition is not met, the access (tCAC) from the CAS clock active transition will determine read access time. The external CAS signal is ignored until an internal RAS signal is available, as noted in the functional block diagram, Figure 24. This gating feature on the CAS clock will allow the external CAS signal to become active as soon as the row address hold time (tRAH) specification has been met and defines the tRCD minimum specification. The time difference between tRCD minimum and tRCD maximum can be used to absorb skew delays in switching the address bus from row to column addresses and in generating the CAS clock.

Once the clocks have become active, they must stay active for the minimum (tRAS) period for the  $\overline{RAS}$  clock and the minimum (tCAS) period for the CAS clock. The RAS clock must stay inactive for the minimum (tpp) time. The former is for the completion of the cycle in progress, and the latter is for the device internal circuitry to be precharged for the next active cycle.

Data out is not latched and is valid as long as the CAS clock is active; the output will switch to the three-state mode when the CAS clock goes inactive. The CAS clock can remain active for a maximum of 10 ns (tCRP) into the next cycle. To perform a read cycle, the write (W) input must be held at the VIH level from the time the CAS clock makes its active transition (tRCS) to the time when it transitions into the inactive (t<sub>RCH</sub>) mode.

#### WRITE CYCLE

A write cycle is similar to a read cycle except that the Write (W) clock must go active (VIL level) at or before the CAS clock goes active at a minimum tWCS time. If the above condition is met, then the cycle in progress is referred to as a early write cycle. In an early write cycle, the write clock and the data in is referenced to the active transition of the CAS clock edge. There are two important parameters with respect to the write cycle: the column strobe to write lead time (tCWI) and the row strobe to write lead time (tRWL). These define the minimum time that RAS and CAS clocks need to be active after the write operation has started ((W) clock at V<sub>IL</sub> level).

It is also possible to perform a late write cycle. For this cycle the write clock is activated after the CAS goes low which is beyond twcs minimum time. Thus the parameters tCWL and tRWL must be satisfied before terminating this cycle. The difference between an early write cycle and a late write cycle is that in a late write cycle the write (W) clock can occur much later in time with respect to the active transition of the CAS clock. This time could be as long as 10

microseconds –  $[t_{RWL} + t_{RP} + 2T_t]$ .

At the start of a write cycle, the data out is in a three-state condition and remains inactive throughout the cycle. The data out remains three-state because of the active transition of the write (W) clock prevents the CAS clock from enabling the data-out buffers as noted in Functional Block Diagram. The three-state condition (high impedence) of the Data Out Pin during a write cycle can be effectively utilized in systems that have a common input/output bus. The only stipulation is that the system use only early write mode operations for all write cycles to avoid bus contention.

#### READ-MODIFY-WRITE AND READ-WHILE-WRITE CYLES

As the name implies, both a read and a write cycle is accomplished at a selected bit during a single access. The readmodify-write cycle is similar to the late write cycle discussed above.

For the read-modify-write cycle a normal read cycle is initiated with the write  $(\overline{W})$  clock at the V<sub>IH</sub> level until the read data occurs at the device access time (tRAC). At this time the write (W) clock is asserted. The data in is setup and held with respect to the active edge of the write clock. The cycle described assumes a zero modify time between read and write.

Another variation of the read-modify-write cycle is the read-while-write cycle. For this cycle, the following parameters (tRWD, tCWD) play an important role. A readwhile-write cycle starts as a normal read cycle with the write (W) clock being asserted at minimum tRWD or minimum tCWD time, depending upon the application. This results in starting a write operation to the selected cell even before data out occurs. The minimum specification on tRWD and tCWD assure that data out does occur. In this case, the data in is set up with respect to write (W) clock active edge.

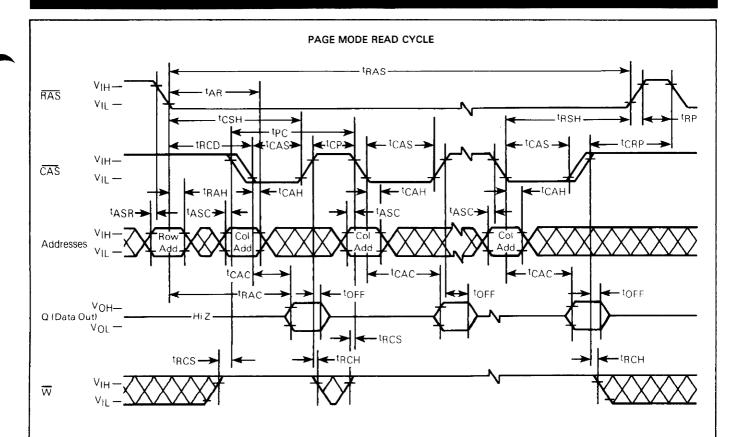

#### **PAGE-MODE CYCLES**

Page mode operation allows faster successive data operations at the 256 column locations. Page access (tCAC) is typically half the regular RAS clock access (tRAC) on the Motorola 64K dynamic RAM. Page mode operation consists of holding the RAS clock active while cycling the CAS clock to access the column locations determined by the 8-bit column address field. There are two controlling factors that limit the access to all 256 column locations in one RAS clock active operation. These are the refresh interval of the device (2 ms/128 = 15.6 microseconds) and the maximum active time specification for the RAS clock (10 microseconds). Since 10 microseconds is the smaller value, the maximum specification of the RAS clock on time is the limiting factor of the number of sequential page accesses possible. Ten microseconds will provide approximately 50 successive page accesses (10 microseconds + page mode cycle time) for each row address selected before the RAS clock is reset.

The page cycle is always initiated with a row address being provided and latched by the RAS clock, followed by the column address and CAS clock. From the timing illustrated, the initial cycle is a normal read or write cycle, that has been previously described, followed by the shorter CAS cycles (tpc). The CAS cycle time (tpc) consists of the CAS clock active time (t<sub>CAS</sub>), and <del>CAS</del> clock precharge time (t<sub>CP</sub>) and two transitions. In addition to read and write cycles, a readmodify-write cycle can also be performed in a page mode operation. For a read-modify-write or read-while-write type cycle, the conditions normal to that mode of operation will apply in the page mode also. The page mode cycle illustrated show a series of sequential reads separated by a series of sequential writes. This is just one mode of operation. In practice, any combination of read, write and read-modify-write cycles can be performed to suit a particular application.

#### REFRESH CYCLES

The dynamic RAM design is based on capacitor charge storage for each bit in the array. This charge will tend to

degrade with time and temperature. Therefore, to retain the correct information, the bits need to be refreshed at least once every 2 ms. This is accomplished by sequentially cycling through the 128 row address locations every 2 ms, or at least one row every 15.6 microseconds. A normal read or write operation to the RAM will serve to refresh all the bits (256) associated with that particular row decoded.

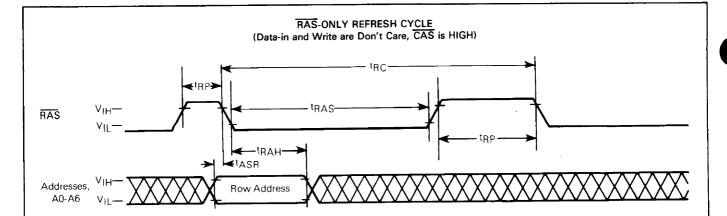

RAS Only Refresh — When the memory component is in standby the RAS only refresh scheme is employed. This refresh method performs a RAS only cycle on all 128 row addresses every 2 ms. The row addresses are latched in with the RAS clock, and the associated internal row locations are refreshed. As the heading implies, the CAS clock is not required and should be inactive or at a VIH level to conserve power.

Auto Refresh Mode and Self Refresh mode (MCM6664A only) — With the MCM6664A, two additional refresh methods are available to the user. These special functions are incorporated on pin 1 of the device and have been approved by JEDEC as an alternative function for that pin on the 64K dynamic memory. The auto refresh mode is accomplished by asserting pin 1 active (VIL level) during the

time interval when there are no memory cycles. In the auto refresh mode, the REFRESH active pulse (tpp) must be limited to 2 microseconds or less. The 2 microsecond time is specified to prevent the device from transitioning into the self refresh mode. Auto refresh can be performed in a distributed mode (refresh cycle every 15.6 microseconds) and in a burst mode where all 128 refresh cycles are done one after the other until complete. An onboard address counter generates the internal row address to refresh a particular row and increments itself at the end of each cycle.

Another variation of refresh is the self refresh mode. This mode is similar to the auto refresh method except that the active pulse width (tFBP) must be greater than 2 microseconds or held down active indefinitely. With pin 1 in the self refresh mode, an internal row address is generated by the internal refresh counter approximately every 15.6 microseconds. This mode of refresh is used for systems requiring battery back-up, and saves additional system power by not requiring an external refresh address counter and address buffers. The power dissipation for either REFRESH mode is the same.

Motorola reserves the right to make changes to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

|           |                    | M                                            | ICM6664A BIT ADD | RESS MAP            |                                              |                                                       |                            |                                 |                            |                  |                                 |                            |                            |                                 |

|-----------|--------------------|----------------------------------------------|------------------|---------------------|----------------------------------------------|-------------------------------------------------------|----------------------------|---------------------------------|----------------------------|------------------|---------------------------------|----------------------------|----------------------------|---------------------------------|

|           |                    | Row Address A7 A6 A!<br>Column Address A7 A6 |                  |                     | Pin 8                                        |                                                       | c                          | Colum                           | ın Ad                      | dress            | es                              |                            |                            |                                 |

|           |                    | F                                            | low              |                     | Hex                                          |                                                       |                            |                                 | A3                         |                  |                                 |                            |                            | A1                              |

|           |                    |                                              |                  |                     | FE<br>FF<br>FC<br>FD<br>FA<br>FB<br>F8<br>F9 | 254<br>255<br>252<br>253<br>250<br>251<br>•248<br>249 | 1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1 | 1 1 1 1 1 1 1    | 1<br>1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>0<br>0<br>0 | 1<br>0<br>0<br>1<br>1<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0 |

|           |                    |                                              |                  |                     | CO                                           | 192                                                   |                            | ۰1                              | 0                          | 0                | 0                               | 0                          | 0                          | 0                               |

|           |                    |                                              |                  |                     | BF<br>BE                                     | 193<br>191<br>190                                     | 1 1 1                      | 0<br>0                          | 1                          | 1 1              | 0<br>1<br>1                     | 1 1                        | 0<br>1<br>1                | 1 0                             |

|           | ir es. ses         |                                              |                  |                     | 83<br>82<br>81<br>80                         | 131<br>130<br>129<br>128                              | 1<br>1<br>1                | 0<br>0<br>0                     | 0<br>0<br>0                | 0<br>0<br>0      | 0<br>0<br>0                     | 0<br>0<br>0                | 1<br>1<br>0<br>0           | 1<br>0<br>1<br>0                |

|           | Column Addresses   |                                              |                  |                     | 7E<br>7F<br>7C                               | 126<br>127<br>124<br>•                                | 0<br>0<br>0                | 1 1 1                           | 1<br>1<br>1                | 1 1 1            | 1 1 1                           | 1<br>1<br>1                | 1<br>1<br>0                | 0<br>1<br>0                     |

|           |                    |                                              |                  |                     | 42<br>43<br>40<br>41                         | 66<br>67<br>64<br>65                                  | 0<br>0<br>0                | 1<br>1<br>1                     | 0<br>0<br>0                | 0<br>0<br>0      | 0<br>0<br>0                     | 0<br>0<br>0                | 1<br>1<br>0                | 0<br>1<br>0                     |

|           | 01 FF              |                                              |                  | 0110                | 3F<br>3E<br>3D                               | 63<br>62<br>61<br>•                                   | 0<br>0<br>0                | 0 0                             | 1 1 1                      | 1<br>1<br>1      | 1 1                             | 1<br>1<br>1                | 1 0                        | 1 0 1                           |

|           | 00 PF              |                                              |                  | 0100<br>1100        | 04<br>03<br>02<br>01<br>00                   | 4<br>3<br>2<br>1<br>0                                 | 0<br>0<br>0<br>0           | 0 0 0 0                         | 0<br>0<br>0<br>0           | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0                | 1<br>0<br>0<br>0           | 0<br>1<br>1<br>0           | 0<br>1<br>0<br>1                |

|           | <b>첫</b> 분 분       |                                              | 75               | 88288               |                                              |                                                       |                            | •                               | •                          |                  |                                 | Ť                          |                            | Ü                               |

| Addresses | <b>Dec</b> 254 255 |                                              | 127              | • • • • • • • • • • | 0 - 3                                        |                                                       |                            |                                 |                            |                  |                                 |                            |                            |                                 |

| , Add     | 9∘-                |                                              | 0                | 0000                | 0                                            |                                                       |                            |                                 |                            |                  |                                 |                            |                            |                                 |

| Row       | 3                  |                                              |                  | 000-                | -00                                          |                                                       |                            |                                 |                            |                  |                                 |                            |                            |                                 |

|           | ₫                  |                                              |                  | 00                  | 000                                          |                                                       |                            |                                 |                            |                  |                                 |                            |                            |                                 |

|           | A                  |                                              |                  | -00000              | 000                                          |                                                       |                            |                                 |                            |                  |                                 |                            |                            |                                 |

|           | * *                |                                              |                  | 00000               |                                              |                                                       |                            |                                 |                            |                  |                                 |                            |                            |                                 |

|           | &                  |                                              |                  | 000000              |                                              |                                                       |                            |                                 |                            |                  |                                 |                            |                            |                                 |

| Pin 16    | A                  |                                              | 00               | 000000              |                                              |                                                       |                            |                                 |                            |                  |                                 |                            |                            |                                 |

Data Stored = Din & Aox & Aix

| Column<br>Address<br>A1 | Row<br>Address<br>A0 | Data<br>Stored |

|-------------------------|----------------------|----------------|

| 0                       | 0                    | True           |

| 0                       | 1                    | Inverted       |

| 1                       | 0                    | Inverted       |

| 1                       | 1                    | True           |

**MOTOROLA** Semiconductor Products Inc.

3501 ED BLUESTEIN BLVD., AUSTIN, TEXAS 78721 ◆ A SUBSIDIARY OF MOTOROLA INC. -